嵌入式培训

达内IT学院

400-996-5531

我们与电子产品之间的关系越来越紧密,这使我们能够获得更高效率和更高生产力。由于在工艺、处理器和嵌入式技术等方面所取得的进步,我们与数字领域的关系越来越近。对于嵌入式设计人员而言,这并非没有问题,他们在设计新产品时面临着无数挑战。其中包括:时钟速度和存储器存取时间无法再大幅度提高,而性能需求却在持续增加;功耗预算不再增加甚至还在下降,而应用功能却在不断增加;此外,在十分广泛的嵌入式应用中对混合信号处理的需求日益增长。高效地应对这些挑战需要一种新型的嵌入式处理器,它不但应当提供非常高的性能水平,而且在实现这一目标时还应当有效地平衡功耗需求并应当支持RISC和信号处理功能的混合,这些功能对于许多嵌入式应用都在变得必不可少。

嵌入式设计挑战

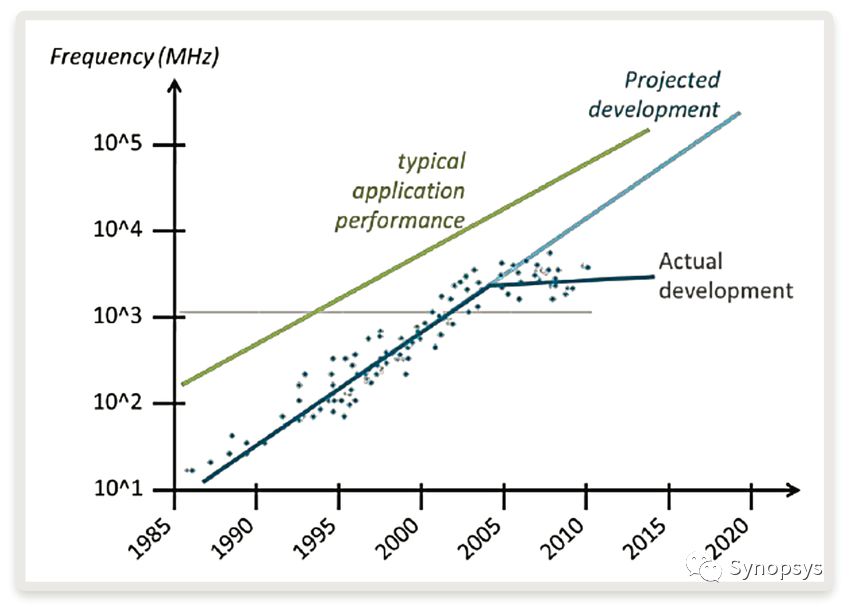

指望再出现下一个工艺节点让你能够用一半的功耗把时钟速度提高一倍,这种时代恐怕是一去不复返了。大多数嵌入式设计的时钟速度已经达到很高程度,处于1 GHz至2 GHz的范围内,如图1所示。尽管速度仍然小幅提高,但我们仅仅通过提高时钟频率来获得更高性能的能力已经很有限了,这是因为我们面临功耗和工艺的限制。这为嵌入式设计人员带来了挑战,因为应用的性能需求一直在不断增加。

图1:处理器性能的增长历史(资料来源:#)

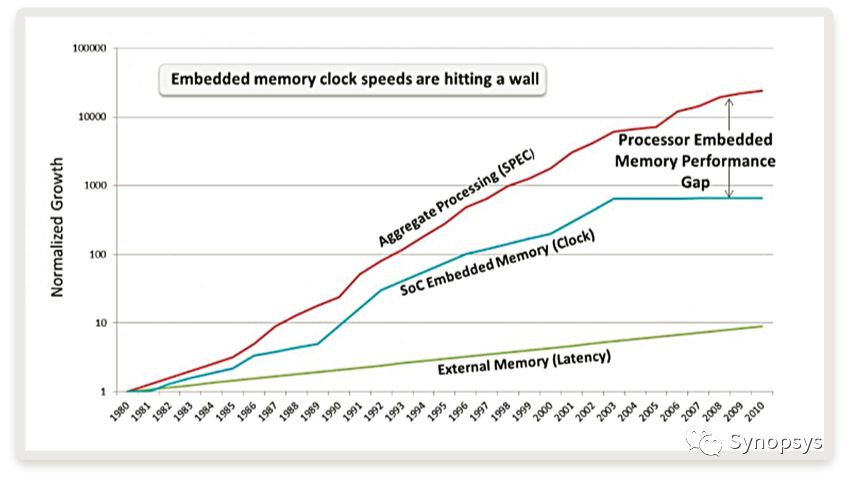

这种挑战由于内存性能差距的扩大进一步加剧(图2)。当我们向下移动工艺曲线时,逻辑速度(图2 -- 红线)的提升速度远远快于内存存取时间(蓝线)。例如,在28nm工艺节点中,逻辑可以以超过3GHz时钟的速度运行,但内存存取速度在最佳条件下也仅限于1.4GHz。从图2可以看出,内存存取时间相当平坦。

图2:嵌入式内存的性能差距(资料来源:#)

内存存取时间将会限制处理器时钟的最大速度,因为处理器运行速度不能比其存取内存的速度更快。

嵌入式设计中的时钟速度也可以进行调节以管理功耗。特别是在电池供电的应用中,功耗预算是固定的,或者只能稍微增长,而性能、功能和特性的要求却在不断增加。即便在功耗似乎不是问题的应用中,功耗预算甚至也受到限制。例如,在汽车中,交流发电机发出的电力是很大的,但每个模块的功率也必须受到限制,以控制整体电力消耗,因为汽车中的电子元件增加非常迅猛。嵌入式应用的功耗设计挑战并不是什么新鲜事,但随着设计日益复杂,对它们的管理变得越来越困难。

因此,需要采用先进的处理器来解决这些嵌入式挑战,但即使是处理器也面临着满足更多要求的挑战。在过去,如果在设计中需要信号处理,就增加一个DSP协处理器,但现在为了提高处理效率,协处理器的功能已经被纳入RISC处理器之中。这种功能的合并减少了设计中的处理器数量,从而节省了功耗,但同时也对性能造成了压力,因为RISC处理器现在需要执行多项任务。

解决这些挑战

这些挑战令人望而生畏,但新型嵌入式处理器提供的功能将帮助设计人员克服这些挑战。虽然嵌入式设计的时钟速度并没有提高,但由于最新的嵌入式处理器可以在每个时钟周期内支持更多的指令,所以性能不断提高。此外,由于能够并行发布和执行多个指令,即多线程功能,这也将提高处理器的性能,而无需提高频率。另一种方法是在对称或非对称配置中使用多核处理器。这些方法使得能够更多地并行完成工作,从而提高性能和吞吐量。

但是,增加每个时钟周期内完成的工作并不能解决内存存取限制的问题。内存存取速度与逻辑速度之间日益扩大的差距对于那些在其流水线(pipeline)中只允许一个阶段(stage)存取内存的处理器有着最深刻的影响。在28 m工艺中,内存存取速度将把处理器的 最优状态下最大时钟速度限制在1 GHz或更低范围内。具有单周期内存存取的处理器几乎没有什么办法来克服时钟速度限制。更新型的高性能嵌入式处理器提供了两个或更多个内存存取周期,这样一来,内存就可以并行地存储(bank)和存取。通过双周期内存存取方式,处理器可以以两倍于内存的速度运行,并在所有工艺节点(包括较新的高级节点)中实现更高的最大时钟速度。

但遗憾的是,在提高处理器性能时,无论是采用增加每时钟周期内指令数量的方法,还是采用多核处理器,亦或是以更高的速度运行处理器以便利用多周期内存存取,这些方法都会大量消耗功耗,这对于功耗预算受限的设计来说是一个大问题。嵌入式处理器的设计人员不能再像过去那样在遇到需要提高性能和吞吐量的问题时就堆砌晶体管。性能的任何提高都必须与如影随形的功耗上升相平衡。因此,嵌入式处理器现在是根据能效比来衡量的,而不是根据单纯的性能或者功率来衡量。在以每微瓦性能(DMIPS/W,CoreMark/W,等等)来衡量时,能效比必须被视为任何新型嵌入式处理器的一项关键设计指标。仔细平衡的能效比能够让嵌入式应用设计人员充分利用处理器性能的提升,同时又能够限制功耗的增加。

当然,能效比并不是控制功耗的唯一途径。新的嵌入式处理器能够让设计人员更好地控制处理器如何使用电力。创建电源岛(island)并对处理器中的功耗进行动态控制的能力有助于设计人员实现其片上系统(SoC)功耗目标。另外在指令集和编译器优化方面有着显著的进步,这能够提高嵌入式代码的密度。嵌入式代码规模减少10%或更多将可以减少内存需求,并在许多情况下节省相比处理器本身 更多的电力。

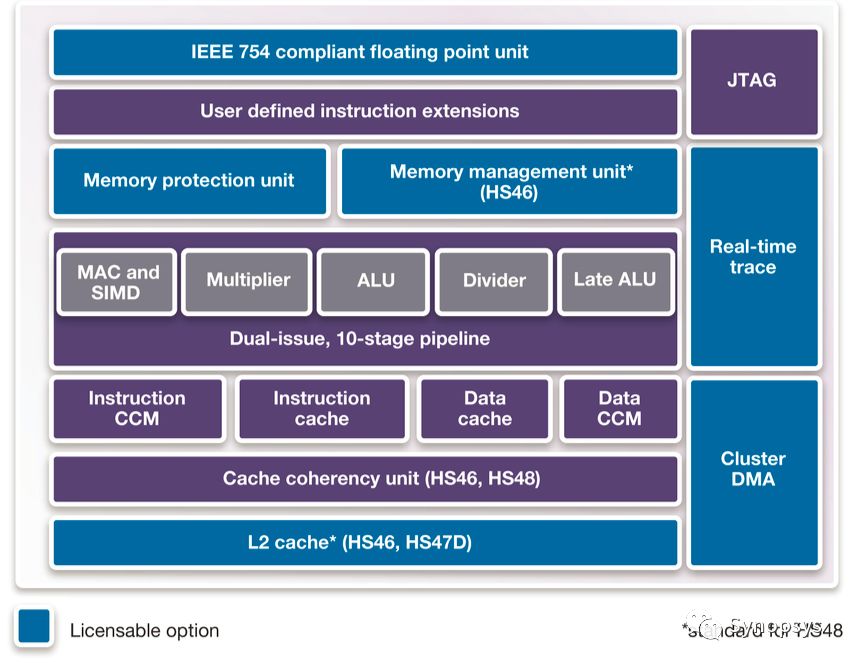

新型超标量ARC HS4x系列

自2013年以来,广泛部署的DesignWare® ARC® HS3x系列高性能处理器已经面市,并且自那时以来,设计挑战也在不断增长。为了帮助设计人员解决这些新兴挑战,Synopsys推出了新型ARC HS4x/D系列。此新系列有五个成员(HS44、HS45D、HS46、HS47D和HS48),并具有针对嵌入式应用优化的双发射(dual-issue)流水线(图3)。结果,与HS3x系列相比较,混合信号HS4x/D系列把RISC性能提高了25%,把信号处理性能提高了一倍,而实现这些成就时,功耗和面积仅增加了15%。此新系列与HS3x系列完全兼容,并提供了双周期内存存取能力,使得内核可以在28 m工艺上以高达2.2 GHz的时钟频率运行。HS45D和HS47D处理器支持150个DSP指令,并提供了非常高水平的RISC和DSP组合性能。为了使新的HS4x内核易于使用,RISC和DSP功能都可以在Synopsys的ARC MetaWare编译器基础上用C/C++语言高效编程,从而能够自动利用处理器的双发射功能最大限度提高性能。

结论

时代正在变化,不断为我们周围的电子世界带来更有趣的功能。技术的进步将把和自然的连接无缝带入这个数字世界,从而提高效率、增加生产力、密切与他人的联系。这些进步也同时给嵌入式设计人员带来了挑战,他们需要采用新方法来应对日益增长的性能和功能的要求,也需要新方法在这些新要求与一直存在的功耗限制之间进行平衡。成功应对这些挑战并实现这一类新型电子产品将需要嵌入式处理器方面的进步。例如,Synopsys新推出的HS4x/D系列产品就能够提供所需要的性能和功能,同时也兼顾了能效比,所以,它不会耗尽你的功耗预算。

本文内容转载自网络,本着传播与分享的原则,来源/作者信息已在文章顶部表明,版权归原作者所有,如有侵权请联系我们进行删除!

填写下面表单即可预约申请免费试听!怕钱不够?可就业挣钱后再付学费! 怕学不会?助教全程陪读,随时解惑!担心就业?一地学习,可全国推荐就业!

Copyright © Tedu.cn All Rights Reserved 京ICP备08000853号-56  京公网安备 11010802029508号 达内时代科技集团有限公司 版权所有

京公网安备 11010802029508号 达内时代科技集团有限公司 版权所有