嵌入式培训

达内IT学院

400-996-5531

一、工作状态

1、ARM状态

此时ARM处理器工作于32位指令状态,所有指令均为32位宽度。

2、Thumb状态

此时ARM处理器工作于16位指令状态,所有指令均为16位宽度。代码密度大,占用的内存空间小。

对于特殊情况下必须执行ARM状态,如异常处理时,需将Thumb状态切换至ARM状态。

对于具有Thumb-2指令集的处理器,Thumb-2就是其Thumb状态。

3、调试状态

补充:

1)Cortex-M仅支持Thumb-2指令集,不支持32位ARM指令集。

2)除Cortex-M处理器之外,其他ARM处理器复位后开始执行代码时总是处于ARM状态

3)对于具有ARM状态与Thumb状态的处理器,状态的切换依赖于指令BX(BLX) Rn,寄存器Rn的最低位控制CPSR(当前状态控制寄存器)的T位,当Rn[0]=0,执行指令BXRn后,CPSR中的T位自动被清零,修改当前状态置于ARM状态。当Rn[0]=1,修改当前状态置于Thumb状态

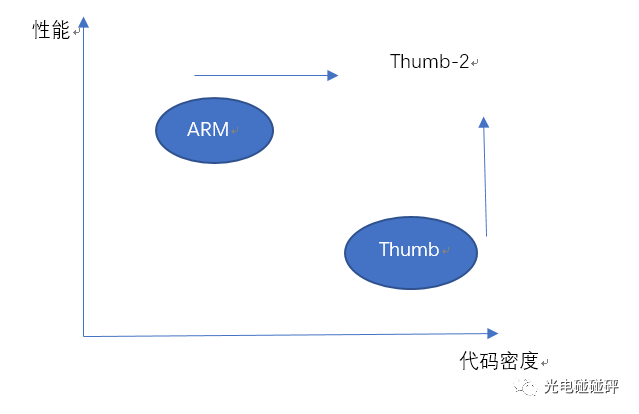

4)ARM、Thumb、Thumb-2状态简单比较

二、寄存器组织

不同的cortex处理器型号有着不同的寄存器组织,若依据工作状态划分可划分为ARM状态下的寄存器组织、Thumb状态下的寄存器组织、Thumb-2状态下的寄存器组织。

下图为ARM状态下的寄存器组织,以cortex-M4为例

下图为Thumb-2状态下的寄存器组织,以cortex-M4为例

三、异常类型

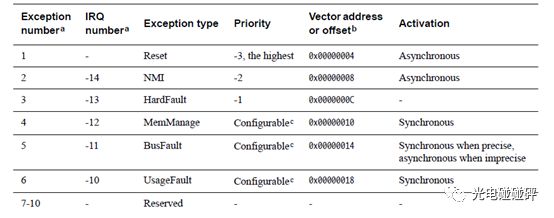

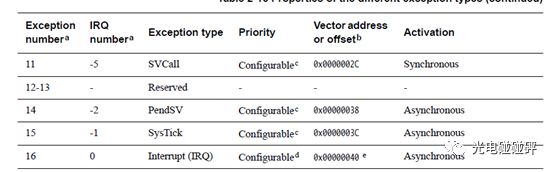

Cortex-M4定义了以下异常类型:复位、NMI(不可屏蔽中断请求)、HardFault(异常响应错误)、MemManage(存储器管理)、BusFault、UsageFault、SVC、PendSV、SysTick(滴答计时)、IRQ(外部中断请求),如图为其详细信息

其中断向量表如图

四、存储器格式

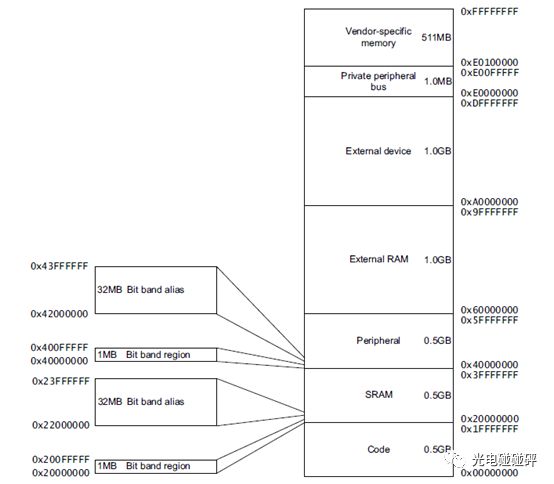

在ARM中,定义32位为字数据,16位为半字数据,8位为字节数据,带FPU的处理器还支持浮点数据。作为32位处理器,cotex-M所支持的最大寻址空间为4GB(2的32次方B)

从图中可以看到,与Intel x86 I/O端口的独立编址不同,ARM采用存储器映像编址方式,对I/O端口等外设采用统一编址。

独立编址的优缺点:采用独立的I/O指令,系统运行速度快,且不占用存储器内存空间。但,由于采用独立的I/O指令,程序设计的灵活性差。

存储器映象编址的优缺点:I/O端口与存储器统一编址,存储器指令同样适用于I/O端口,可对I/O端口作众多复杂性操作,程序的灵活性好。但,由于I/O端口占用了内存空间,使得内存空间减少。

ARM有两种存储数据字的格式:大端模式(Big-Endian)、小端模式(Little-Endian)。

1)大端模式

在这种模式下,32位数据字以字节为最小单位划分,高字节存放在低地址中,低字节存放在高地址中。

2)小端模式

在这种模式下,32位数据字以字节为最小单位划分,低字节存放在低地址中,高字节存放在高地址中。

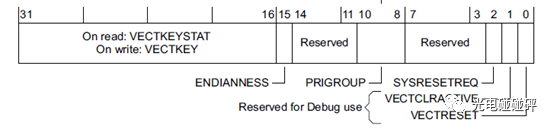

可通过AIRCR寄存器(ApplicationInterrupt and Reset Control Register)的第15位来设定。ENDIANNESS=0时,小端模式;ENDIANNESS=1时,大端模式。

最后,简单谈一下微处理器经常使用的两种技术:MMU(存储器管理单元)和MPU(存储器保护单元)。MMU部件能把系统中不同类型的存储器(SRAM、Flash、SDRAM、ROM等)进行统一管理,通过地址映射,使需要运行在连续地址空间的软件可运行在不连续的物理存储器中,需要较大存储空间的软件可运行在较小容量的物理存储器中,此即虚拟存储器技术。MMU完成了虚拟地址到物理地址的映射。

MPU是对存储器进行保护的可选部件,它提供了简单代替MMU的方法来管理存储器。在ARM中,MPU允许4GB地址空间定义为8个段,分别控制八个指令和八个数据内存块,段与段之间可以重叠,每个段的地址与长度均可编程,且段起始地址必须是其大小的整数倍、段的长度可以是4KB-4GB之间任意一个2的指数。(这与Intel x86系列的分段管理存储器的方法较为类似,只是相较于程序,仍需深刻理解)

本文内容转载自网络,本着传播与分享的原则,来源/作者信息已在文章顶部表明,版权归原作者所有,如有侵权请联系我们进行删除!

填写下面表单即可预约申请免费试听!怕钱不够?可就业挣钱后再付学费! 怕学不会?助教全程陪读,随时解惑!担心就业?一地学习,可全国推荐就业!

Copyright © Tedu.cn All Rights Reserved 京ICP备08000853号-56  京公网安备 11010802029508号 达内时代科技集团有限公司 版权所有

京公网安备 11010802029508号 达内时代科技集团有限公司 版权所有