嵌入式培训

达内IT学院

400-996-5531

一、区别

两则的分流造成的主要原因是数字信号处理的简便性,考虑一个数字信号处理的实例,比如有限冲击响应滤波器(FIR)。用数学语言来说,FIR滤波器是做一系列的点积。取一个输入量和一个序数向量,在系数和输入样本的滑动窗口间作乘法,然后将所有的乘积加起来,形成一个输出样本。

类似的运算在数字信号处理过程中大量的重复发生,使得为此设计的器件必须提供专门的支持,促进了DSP器件与通用处理器(GPP)的分流:

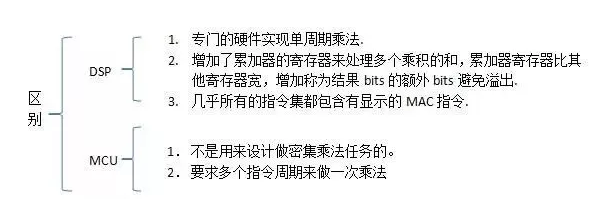

1. 对密集乘法的支持

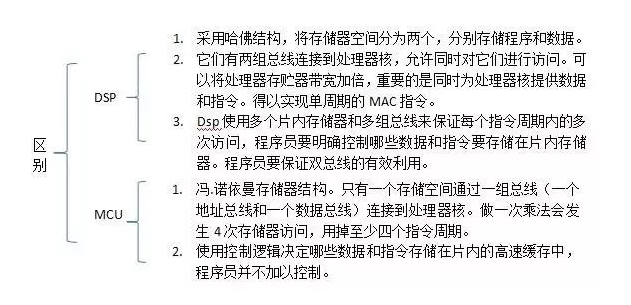

2. 存储器结构:

此外,DSP处理器几乎都不具备数据的高速缓存。这是因为DSP的典型数据是数据流。也就是说,DSP处理器对每个数据样本做计算后,就丢弃,几乎不再重复使用。 3. 零开销循环

DSP算法的一个共同的特点,即大多数处理时间都花在执行较小的循环上,也就容易理解,为什么大多数的DSP都有专门的硬件,用于零开销循环。所谓的零开销循环是指处理器在执行循环时,不用花时间去检查循环计数器的值,条件转移到循环大额顶部,将循环计数器减1.

与此相反,GPP的循环使用软件来实现。某些高性能的GPP使用转移预报硬件,几乎达到与硬件支持零开销循环同样地效果。

二、联系

按照传统方式,嵌入式应用中的数字信号处理器(dsp)相对于主微控制器起到从属的作用。在这些应用中,MCU用作系统控制器,而大量的数据处理留给DSP。例如,在音频或视频处理器应用中有可能需要人机界面管理,或则是整个系统的控制。

为完成这些任务,有几种系统设计方案选择

第一种方案是将DSP和MCU芯片组合在印制电路板上。这种方案成本高并且占用面积大,但是可适当地调整每个芯片的尺寸以最大限度的满足系统需要。

第二种方案是将DSP功能合并到一个MCU中。这种方案只适合于直接的信号处理应用。MCU的时钟频率和计算体系结构根本上不太适合大量的数字处理。有些MCU试图通过增加一个乘法和累加器(MAC)(dsp的一个特点)来补偿上述不足。但是这种方案任然缺乏高级应用所需要的基本的“由上至下”的体系结构设计。

第三种方案是一种将dsp和mcu组合在单个封装内的多芯片模块(mcm).这种方案的局限性是,设计工程师必须按“50/50”的时间比例分配给控制和DSP功能;例如,一旦DSP超出时间,MCU不能完成计算任务。像第一种方案选择一样,当DSP和MCU内核独立存在的时候,需要两套开发工具。

已经出现第四种方案它是将MCU的功能合并到一个DSP中。这类方案的一个例子是美国模拟器件公司(Anolog Device Inc.,简称ADI)的Blackfin 处理器系列。这些新型处理器具有统一的经过优化的体系结构,不仅适于数据计算,而且也适于有关的控制任务。通过平衡执行控制任务与复杂计算的要求,这种方案可以根据系统实时处理的需要,完成100%的控制或者100%的计算任务。完成所有这一切任务不需要在DSP模式和MCU模式之间的模式转换。

填写下面表单即可预约申请免费试听!怕钱不够?可就业挣钱后再付学费! 怕学不会?助教全程陪读,随时解惑!担心就业?一地学习,可全国推荐就业!

Copyright © Tedu.cn All Rights Reserved 京ICP备08000853号-56  京公网安备 11010802029508号 达内时代科技集团有限公司 版权所有

京公网安备 11010802029508号 达内时代科技集团有限公司 版权所有