嵌入式培训

达内IT学院

400-996-5531

嵌入式系统概述——硬件篇

一、何为嵌入式系统?

IEEE从应用的角度定义嵌入式系统是“控制、监视或协助设备、机器、工厂运行的装置”。(devices used to control, monitor, or assist the operation ofequipment machinery or plants)

二、嵌入式系统硬件组成

1、最小系统

时钟电路:本质上是同步时序电路,是系统正常工作的必备条件。很多处理器芯片内部都内置了时钟发生器,因此常只需石英晶体和电容便可构成时钟电路。然而很多设备,常常不采用内部时钟信号发生器,而采用外部时钟信号源。

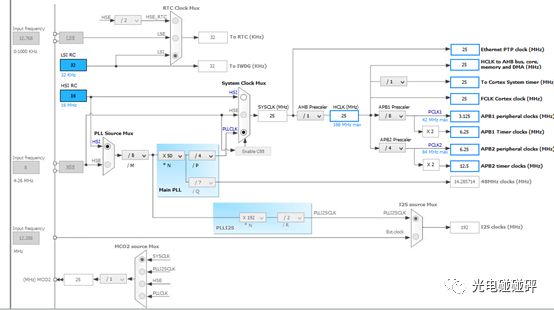

很多处理器芯片都有一个很重要的时钟图,常称其为时钟树,不得不说,时钟树在嵌入式系统开发的过程中起着很重要的角色。如图为ST公司生产的STM32F4的时钟树

电源电路:有三种重要的电源电路,交流-直流模块、直流-直流模块、稳压模块。其中,交流-直流模块起着220V AC到5V DC(3V DC),稳压模块包括普通稳压模块和低压差稳压模块。

复位电路:嵌入式系统芯片都有一个复位引脚,在此引脚保持若干个时钟周期的高(低)电平时,系统才能可靠复位。在对复位的可靠性要求不高时,通常不采用复位芯片而直接用开关接地或接高电平控制。

调试测试接口:ARM芯片内部集成了测试电路,联合调试测试接口(JTAG)是一种国际标准测试协议,主要用于测试芯片及系统内部的仿真与调试。

附:JTAG——片上调试技术

JTAG采用边界扫描测试技术并提供测试访问口(Test Access Port),其被IEEE接纳为IEEE 1149规范(指此边界扫描测试技术和TAP接口)。

JTAG标准中规定TAP接口使用以下5根信号线:

1)TCK:时钟信号线,为TAP

2)TMS:模式选择控制信号线,与TCK配合用于设置TAP控制器的工作状态

3)TDI:数据输入信号线

4)TDO:数据输出信号线

5)TRST:复位信号线

JTAG仿真器

常见的有J-LINK、U-LINK、ST-LINK,其中J-LINK对ARM芯片支持的种类最多、兼容性也最好,因此也被广泛使用。目前最新版的J-LINK v9,受到广泛应用。

其调试模式不仅支持JTAG,还支持SWD模式。

SWD模式是ARM cortex-M内核独有的一种少引脚调试接口,采用串行线调试接口。在调试芯片时,最少连接线数为4根,SWDIO数据线、SWCLK时钟线、GND、VCC。其中GND为共地端,VCC为电源输出端。

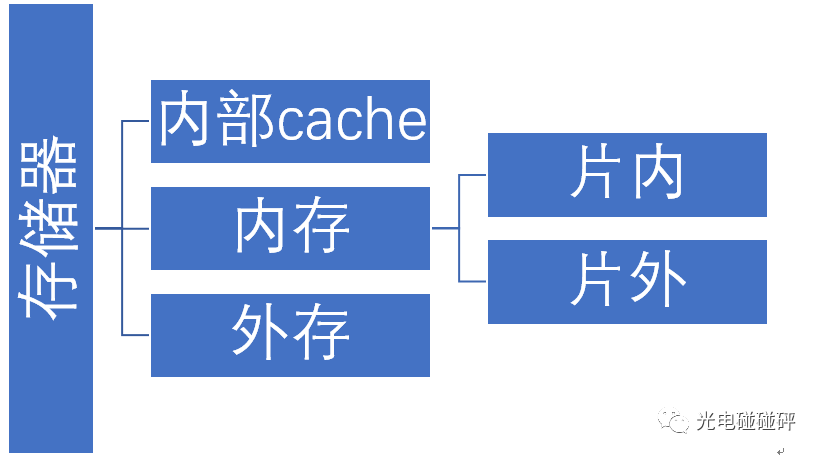

存储器:其层次结构如图所示

嵌入式系统常采用SRAM作为1级Cache和2级Cache。

片内存储器:

1)片内Flash ROM:用来作为程序存储器

2)片内SRAM:作为数据存储器

3)片内E2PROM:用来长期存放重要数据

4)片内FRAM(铁电存储器):目前已经开始应用于微控制器。其具有ROM和RAM的全部特点,既可以当ROM使用,又可以当RAM使用。

片外存储器:

1)片外程序存储器:

以下两种技术是当代主要的闪存技术:

NOR Flash ROM:Intel推出的以字节为单位随机存储,应用程序可以直接在其中执行,不必再把程序代码预先读入到RAM中。其接口简单,可直接连接到处理器的外围总线上。但其读写和擦除速度较慢

NAND Flash ROM:东芝推出的以页(行)为单位随机存储,在容量、使用寿命、成本上具有较大的优势。通常将其作为数据存储器,也可以作为程序存储器使用。U盘是其典型的应用。

2)片外数据存储器:

SDRAM、DDR/DDR2/DDR3/DDR4等。它们都是动态随机存储器,其信息存储都是以MOS管的栅极电容作为存储单元的,电容的充放电状态作为记录信息的0/1,而电容易漏电,这就需要定时刷新电容以保持原来的信息不变。

SDRAM即为同步DRAM,DDR是DDR SDRAM的简称,称其为双倍数据速率同步动态存储器。其特点是在系统时钟触发沿的上升、下降都能进行数据传输,从而把数据传输速率提高了一倍。其数据预读取能力为2位。

DDR2(DDR3)保持了DDR的双边沿触发传输特性,提高了存储器内部时钟工作频率,扩展了数据预读取位数(DDR2为4位,DDR3为8位)。使传输速率提高了2倍(DDR3位4倍)。

DDR4的数据传输速率是DDR3的2倍,且拥有两种规格。一种是以Single-ended Signaling为信号的,传输速率可达到1.6-3.2GB/s,另一种是基于差分信号技术的,其传输速率可达到6.4GB/s。

2、片上系统

众多半导体公司在设计微处理器时,习惯将微处理器内核与AD/DA、中断控制器、DMA控制器、LCD控制器、以太网接口、定时计数组件、通信接口(CAN、IIC、IIS、SPI、USB)等集成在一块芯片之上,使其具有一个计算机系统的特征,称其为片上系统(SoC, System-on-a Chip)。

前面介绍了ARM公司的AMBA总线接口标准,下面对微控制器内核与周围组件连接而构成片上系统作陈述。

AHB系统总线,连接高带宽快速组件,包括ARM内核、电源管理与时钟控制器、调试测试接口、片上存储器、中断控制器、DMA控制器、LCD控制器、USB主机、高带宽外部存储器控制接口、以太网接口等

APB外围总线,主要连接低带宽组件以及与外部相连的硬件组件,包括GPIO、UART、IIC、SPI、IIS、CAN、ADC、DAC、RTC、WDT、TIMER、PWM、USB设备等

AHB与APB通过桥接器连接。

其间每一个步骤都需要不断的设计验证改善,涉及的学问至上至深,有兴趣的读者可翻阅各大半导体公司的芯片手册。

需要强调的是,很多生产厂家在设计SoC时,经常包含多个微处理器内核以使其具有强悍的性能。经常有ARM内核+ARM内核,ARM内核+DSP等,如STM32F4内集成了ARM-MCU与DSP,使其具有强悍的数字信号处理能力,故习惯称其为DSC(digital signal controller)数字信号处理器。

DMA控制器:直接存储器访问控制器。使用它可直接将数据块从外设传输到内存、从内存传输到外设或从内存传输到内存,而不需要CPU参与,从而降低了CPU的负荷。事实上,当DMA向CPU请求总线的控制权时,CPU将总线控制权交给DMA,待数据传输结束后,DMA再将总线控制权交还给CPU。

3、嵌入式硬件系统

由最小系统、前向通道、后向通道、人机交互通道、相互互联通道等组成

最小系统:即前面介绍的六大组成部分

前向通道:即输入接口,包括模拟量输入接口和数字量输入接口

后向通道:即输出接口,包括模拟量输出接口和数字量输出接口

人机交互通道:包括键盘、触摸屏、LED、LCD等

相互互联通道:包括RS-232、RS-485、CAN、USB等诸多通信接口

本文内容转载自网络,本着传播与分享的原则,来源/作者信息已在文章顶部表明,版权归原作者所有,如有侵权请联系我们进行删除!

填写下面表单即可预约申请免费试听!怕钱不够?可就业挣钱后再付学费! 怕学不会?助教全程陪读,随时解惑!担心就业?一地学习,可全国推荐就业!

Copyright © Tedu.cn All Rights Reserved 京ICP备08000853号-56  京公网安备 11010802029508号 达内时代科技集团有限公司 版权所有

京公网安备 11010802029508号 达内时代科技集团有限公司 版权所有